|

NSA@home |

|

The jrev tool tries to automate the process of reverse-engineering the board connectivity. It probes all pairs of JTAG-scannable pins on the board. To use it, you need to make sure that more than one chip on your board has JTAG (you can use it with one chip, but the results will have limited usefulness). Connect a JTAG cable compatible with Xilinx DLC-5 to your board and run jget. Review the stderr output to see if there are unrecognized chips - you might have to create pin description files for them (see the README). Then run the main tool - probably through the tee command to capture it to a file.

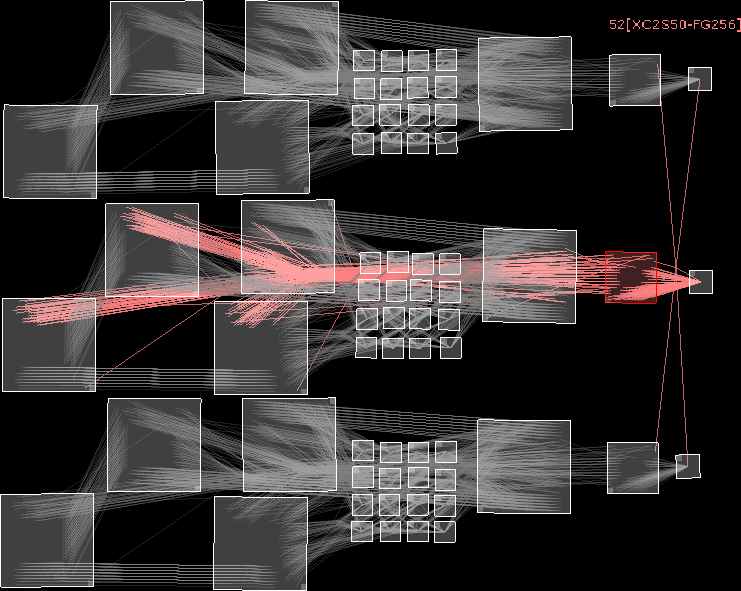

Outputs of jrev can be visualized as interactive rats-nest drawings with jvis. Make sure you have an OpenGL-capable graphics card. If you have an FT2232-based JTAG cable, you can try FTjrev. You need files from the DLC-5 jrev archive above, too. |

(c) 2007 Stanislaw Skowronek

Contact me: nsa unaligned org (figure out where to put the @ and .)

irc.unaligned.org #nsa