|

NSA@home |

|

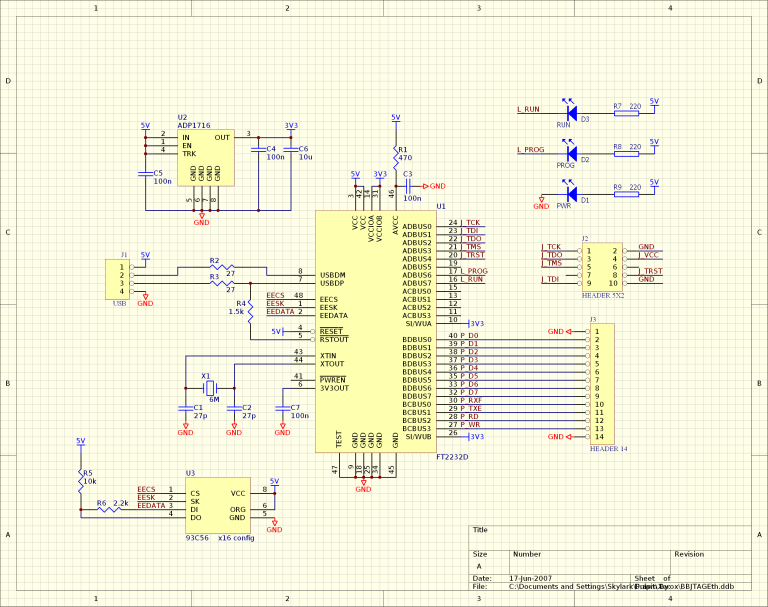

The host PC is connected to the FPGA boards using full-speed USB links. Both programming (JTAG) and workload-related communications use those. A small daughterboard that connects to the JTAG port and a test connector on the FPGA board was designed. The test connector connects to all 3 Spartan-II FPGAs which share the ownership of the USB port through a token-ring protocol. Those FPGAs distribute the workload to the Virtex-II Pro FPGAs through a standard synchronous bus interface and gather results the same way. The USB daughterboard is built around a FT2232C/D chip from FTDI with a 3.3V power regulator. The first port is used in the MPSSE mode, and the second one is used in the 8-bit parallel FIFO mode. FPGA loading runs from SVF files using a trivial utility, ftjsvf. It implements a subset of SVF that is enough to implement Xilinx FPGA loading, plus a special "ALIGN" keyword on SDR commands that allows Spartan-II chips to be loaded anywhere inside the chain. Interestingly, Xilinx IMPACT doesn't load SVF files for Spartan-IIs that aren't the only chips in chain correctly, so some equivalent of this non-standard keyword might be actually needed. You can download ftjsvf here. |

(c) 2007 Stanislaw Skowronek

Contact me: nsa unaligned org (figure out where to put the @ and .)

irc.unaligned.org #nsa